随着电子技术的迅猛发展,时钟信号在数字电路设计中扮演着越来越重要的角色。时钟缓冲器和时钟发生器作为确保稳定时钟信号的两个关键设备,它们各自拥有不同的特性和优势。本文将深入探讨这两种设备的各自优势,以助于工程师在实际应用中做出明智的选择。

一、时钟缓冲器的优势

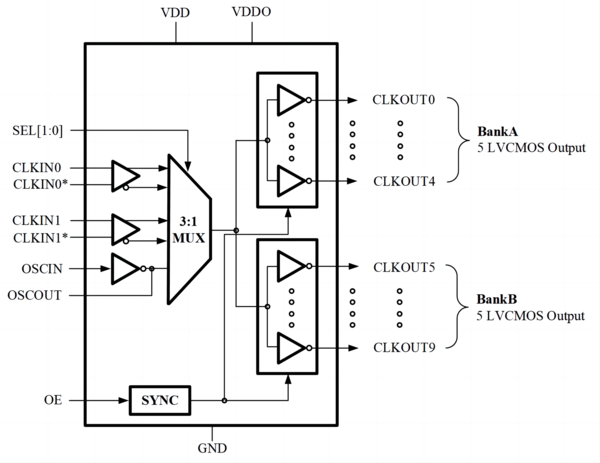

时钟缓冲器主要用于时钟信号的放大与分配,它可以增强原始时钟信号的驱动能力,保证信号到达每一个需要同步的元件。其优势主要体现在以下几个方面:

1. 信号增强:时钟缓冲器能够对输入的时钟信号进行放大,使得信号更加稳定,减少传输过程中可能出现的衰减问题。

2. 多路输出:它能够提供多个输出,使得一个时钟源可以同时驱动多个负载,非常适合大型集成电路中的时钟分配。

3. 降低抖动:通过内部优化的电路设计,时钟缓冲器有助于减小时钟抖动(jitter),提高系统整体的时间精度。

4. 易于集成:现代的时钟缓冲器通常具有体积小、功耗低的特点,易于集成进各种电路板设计之中。

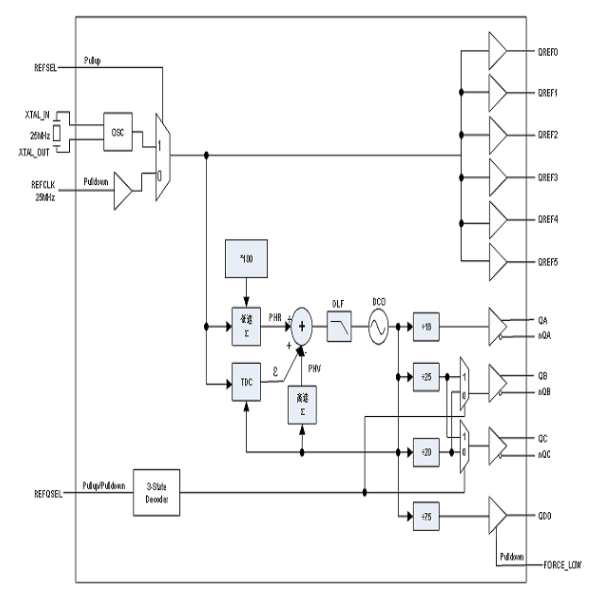

二、时钟发生器的优势

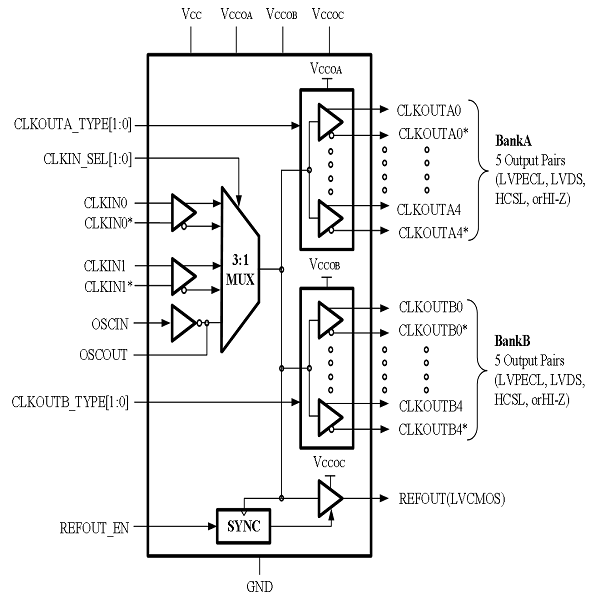

时钟发生器是产生时钟信号的关键部件,它将外部的参考频率转换为内部所需的时钟频率。其主要优势包括:

1. 高精度输出:时钟发生器能产生非常精确的时钟频率,满足高速数字电路对时间精度的高要求。

2. 可调性强:多数时钟发生器具有很好的调节性能,可以根据需求调整输出频率、相位等参数,灵活性高。

3. 稳定性好:高质量的时钟发生器能够在不同温度和电压变化下保持输出的稳定性,适用于各种复杂的环境条件。

4. 多功能性:一些高级时钟发生器还可以提供多种功能,如同步、复位等,为电路设计提供更多可能性。

总结:

在选择时钟缓冲器或时钟发生器时,设计者需要考虑实际的应用场合和需求。若是为了放大和分配现有的时钟信号,时钟缓冲器是一个合适的选择;而如果需要生成一个新的时钟信号或者对现有信号进行精确控制,那么时钟发生器将更为适合。理解它们的各自优势能够帮助设计师更好地优化电路设计,提升系统的整体性能。

时钟系统

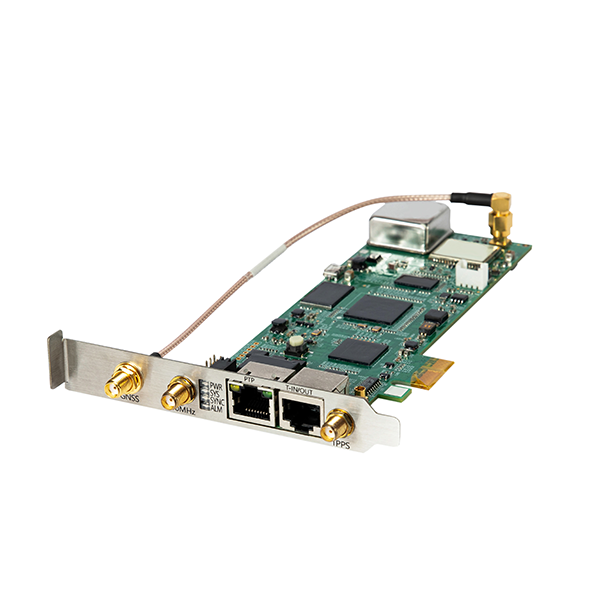

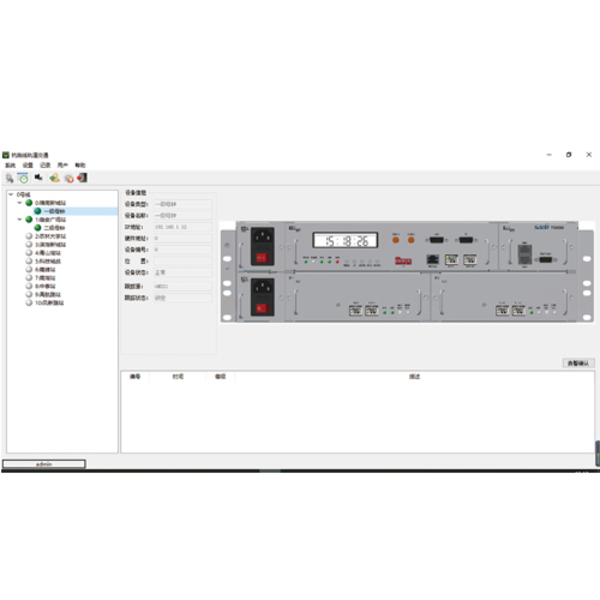

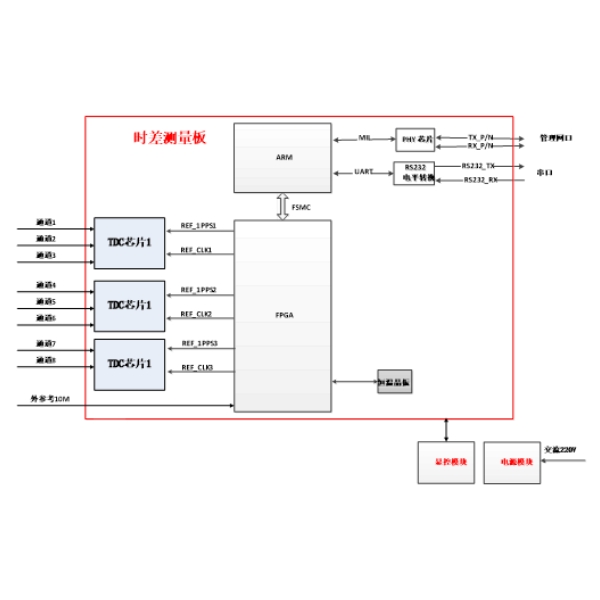

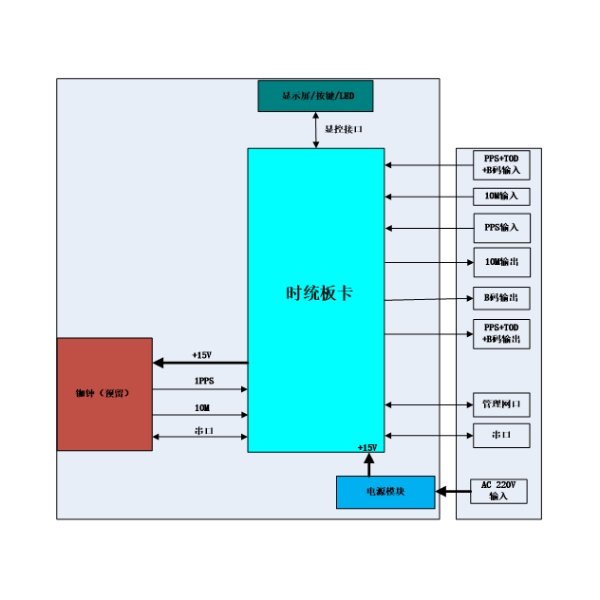

时钟系统  芯片

芯片  晶振&原子钟

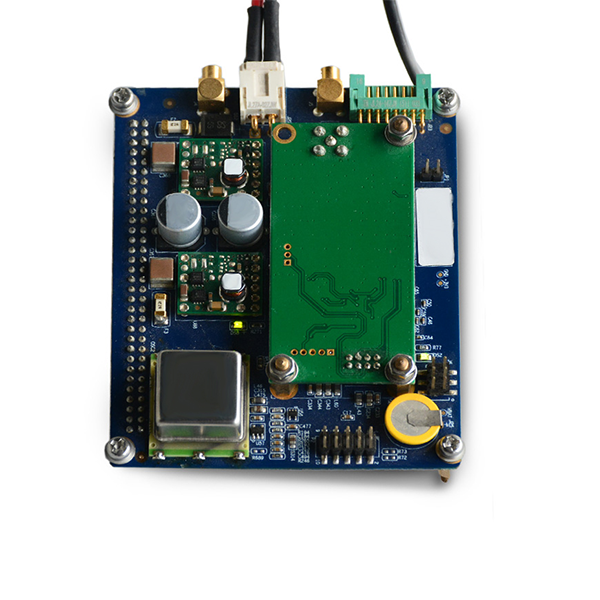

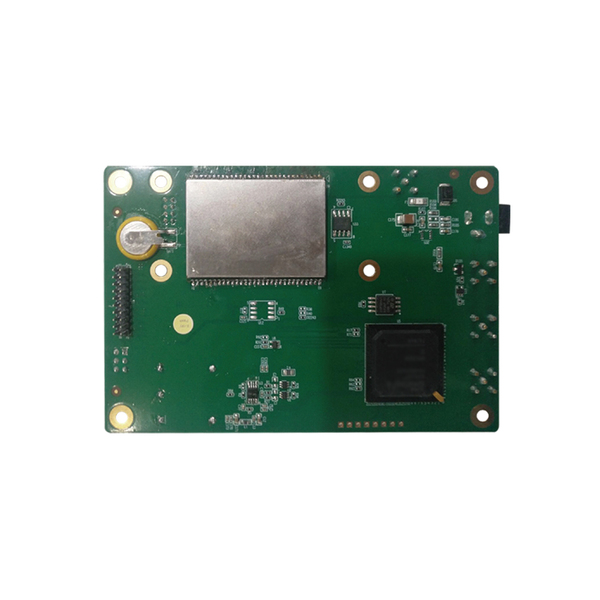

晶振&原子钟  授时板卡 NTP时间同步服务器PTP时间同步服务器时间同步装置授时安全防护装置网同步设备/时频一体化设备子母钟系统BBU池时间同步时统设备钟组设备测试仪器光纤双向设备网管系统语音芯片时钟发生器时钟缓冲器时钟SOC芯片超低噪声OCXO超高稳OCXO小型化OCXO温补晶振TCXO原子钟时钟模块授时模块

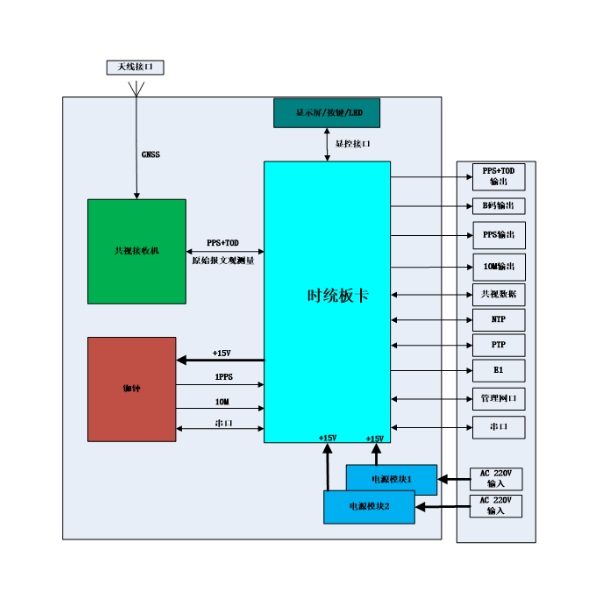

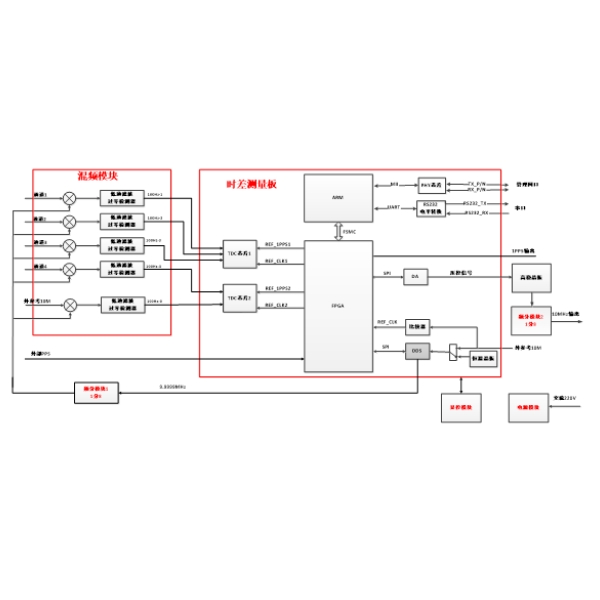

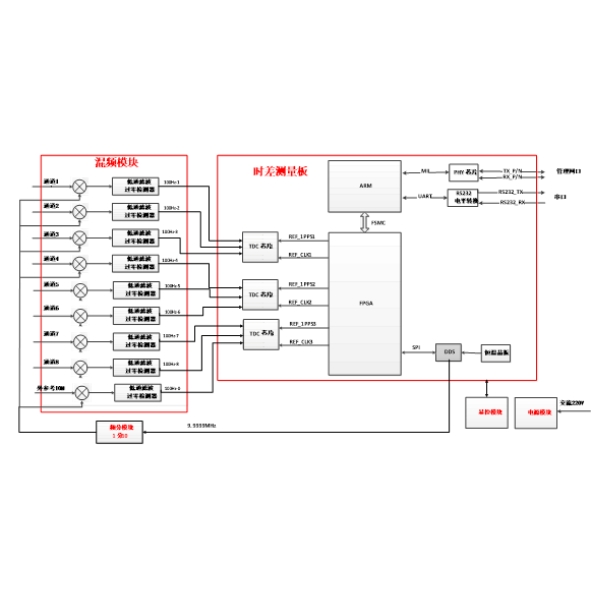

授时板卡 NTP时间同步服务器PTP时间同步服务器时间同步装置授时安全防护装置网同步设备/时频一体化设备子母钟系统BBU池时间同步时统设备钟组设备测试仪器光纤双向设备网管系统语音芯片时钟发生器时钟缓冲器时钟SOC芯片超低噪声OCXO超高稳OCXO小型化OCXO温补晶振TCXO原子钟时钟模块授时模块

智能电网

智能电网

通信网络

通信网络

智慧交通

智慧交通

智能楼宇

智能楼宇

数据中心

数据中心

前沿领域

前沿领域

新闻资讯

新闻资讯

联系我们

联系我们

人才研学中心

人才研学中心

加入赛思

加入赛思

关于赛思

关于赛思